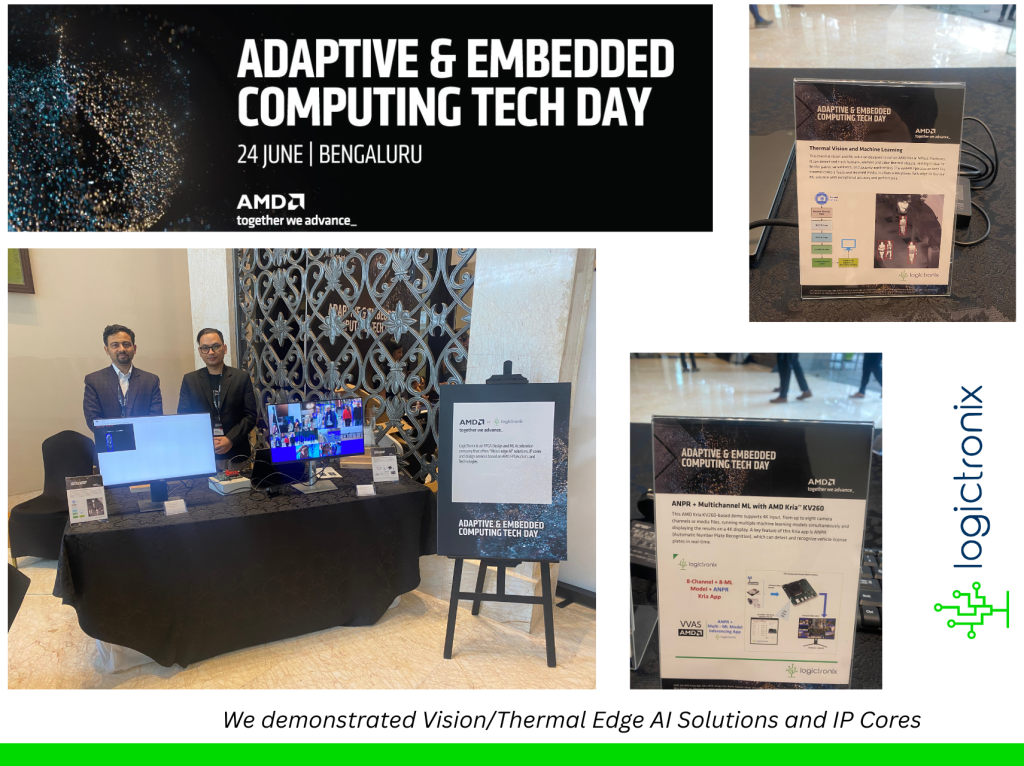

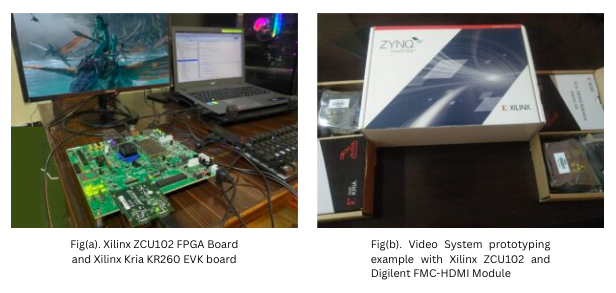

LogicTronix will demonstrate its ADAS sensor fusion, Physical AI, and Thermal Vision IP Core + ML solutions at the AMD Embedded Computing Summit (ECS) in Bangalore and Tokyo in August 2026. Along with our AI-enabled solutions, we will also be demonstrating some of our reference designs and IP cores at the ECS Summit. This marks our third year of participation in the AMD-Xilinx Adaptive and Embedded Computing Summit.

We will be demonstrating at AMD ECS Bangalore at Aug 20th, 2026 and Tokyo at Aug 28th, 2026.

More details , event locations and agendas about the AMD ECS 2026 can be fount here : https://amd.cventevents.com/event/ecs2026/summary

Are you attending AMD ECS 2026 in Tokyo or Bangalore? Visit the LogicTronix booth — we look forward to meeting you there!