LogicTronix is “AMD-Xilinx Adaptive and Embedded Computing Partner” and “Design Service Partner for AI/ML for Kria SoM FPGA”.

Our IP Cores are available at AMD-Xilinx IP Page: www.amd.com/en/search/partner/embedded-partner-solutions.html [search – logictronix]

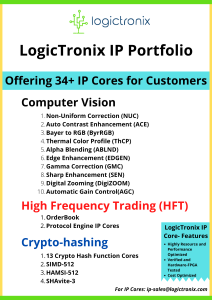

Our FPGA IP Portfolio ranges on following Streams/Applications:

A. Computer/Machine Vision and AI/ML IP Core for FPGA:

- ANPR Solution :

- Real time License Plate Recognition Solution, it is low cost Edge based solution fused with Machine Learning in which our solution detect and recognize the vehicle license plates in real time with the IP camera input. It cost effective solution and can also process multi-stream camera input. Our ANPR solution is deployed for our customers for smart-parking applications in different regions including Asia-Pacific, North America and South-East Asia.

- Non-Uniform Correction (NUC)-IP Core

- NUC IP Core is used by our customer for Machine Vision Application and Thermal Imaging Applications: IP Product Guide- PGL031 and Example Design for Xilinx 7 Series FPGA

- Thermal Color Profile (ThCP)

- ThCP IP core is applied for Machine Vision, Thermal Imaging , Industrial and Biomedical Applications: IP Product Guide-PGL032 and Example Design for Xilinx 7 Series FPGA

- Auto Contrast Enhancement (ACE) IP Core

- ACE IP core is deployed for Thermal Imaging Applications: IP Product Guide-PGL033 and Example design for Xilinx 7 series FPGA

- Bayer to RGB(ByrRGB) IP Core

- ByrRGB IP Core is for Sensor Interfacing, Machine Vision and Sensor Fusion: IP Product Guide-PGL034

- Alpha Blending (ABLND) IP Core

- for blending multiple layer of output on Video Processing: IP Product Guide-PGL036

- Gamma Correction(GMC) IP Core

- for gamma correction on RGB ISP pipeline: IP Product Guide-PGL037

- Sharp Enhancement (SEN) IP Core

- for Video/Image Processing: IP Product Guide- PGL038

- Edge Enhancement (EDGEN) IP Core

- for Video/Image processing: IP Product Guide-PGL039

- Digital Zooming(DigiZOOM) IP Core

- for performing zoom operation Video/Image Processing: IP Product Guide-PGL040

- Automatic Gain Control(AGC) IP Core

- for Camera Streaming, Video Processing , Medical/Thermal/Industrial Vision: IP Product Guide-PGL041

B. LogicTronix Thermal ISP Pipeline IP Core for FPGA

C. Cryptographic Hashing Function – SHA, HAMSI, NIST IP cores

- HAMSI-512 :

- The HAMSI IP Core is a fully pipelined architecture with very high throughput and initiation interval of 1 running at 600MHz. It is one of SHA-3 candidate in NIST hash function competition. Hamsi cryptographic hash function can be used on security, FinTech, Encryption and decryption etc applications.

- SHAvite-3 :

- The SHAvite-3 Core is hash function core running at very high 35.7 GBps throughput with fully pipelined architecture .It is optimized to run at high frequency of 600Mhz in VU9P & VU13P. SHAvite-3’s compression functions are secure against cryptanalysis, while the selected mode of iteration offers maximal security against black box attacks on the hash function. SHAvite-3 is both fast and resource-efficient, making it suitable for a wide range of environments.

- SIMD-512 Hash Core :

- SIMD Core is cryptographic hash function IP core with fully pipelined architecture and it is optimized to run at 600Mhz in VU9P & VU13P. It is designed to operate on 512 bits of input and output. The most important component of SIMD is its message expansion, which is designed to give a high minimum distance.

- 13 Different Cryptographic Hash Functions Core:

- This IP core is bundle of 13 different SHA-3 competitor cryptographic hash functions originally submitted to NIST hash competition.All these cores are fully pipelined & deliver 35.7GBps throughput.

- In this bundle of cores we have SHA-3, Keccak, Blake, Grostl, JH, Skein Cores that got selected for NIST round 3 and BMW, Echo, Shabal, Cubehash, Fugue and Luffa from NIST round 2. We also have Whirlpool hash function on this bundle.

- It is primarily targeted for extremely high throughput applications with input and output width of 512-bit while the Core can be modified for any bit-width and range of applications like Security, FinTech and Encryption/Decryption.

D. High Frequency Trading (HFT) – OrderBook IP Core

- Order Book :

- Ultra-low latency OrderBook for HFT : IP Product Guide [Download].

- The LogicTronix’s orderbook IP provides ultra low latency & area efficient design with 43 ns latency supporting more than 27-73 symbols each with upto 32768 ask/bid orders inside the VU9P FPGA.

- OUCH Protocol Engine IP Core for High Frequency Trading with FPGA [SBL025]: PDF Link

- ITCH Protocol Engine IP Core for High Frequency Trading with FPGA [SBL026] : PDF Link

E. Image/Video Compression – JPEG IP Cores

LogicTronix has developed the highly optimized JPEG compression IP core based on RTL for image compression application targeted for Media/Broadcast/Vision and Edge-AI applications.

- JPEG 2000 encoder IP Core

- JPEG XS encoder IP Core

- IP Core Feature

- Compliant with ISO/IEC 21122-1

- AXI4-Lite control interface

- AXI4-Stream data interfaces

- Color space RGB, YCbCr

- Color Sampling 4:4:4, 4:2:2

- Fixed latency – four lines of pixels

- Programmable compression rate

- Single and dual pixel per clock architectures

- IP Product Guide [PGL011] – PDF Link

- IP Core Feature

- JPEG XL – coming soon

Our compression IP core support all varieties of FPGA devices and vendor tools.

F. Automotive Application- CAN , DSI3 and LIN IP Cores

- AXI CAN FD IP Core

- The CAN FD controller IP is designed to be used in real-time control applications in Automotive and Industrial systems.

- The IP core has configuration registers and mail box buffers; TX buffers and RX buffers. The number of mailboxes in the TX buffer and RX buffer are configurable.

- The TX buffer can be configured up to 32 mailboxes and supports 16 RX mailboxes. Each mailbox at RX buffer is associated with an Acceptance Filter Mask Register for masking the ID of incoming message frames ,so that only desired messages are written in receive message space.

- Features of AXI CAN FD are:

- Designed to ISO 11898-1/2015

- Supports CAN and CAN FD frames

- Supports Nominal bit rate up to 1 Mb/s and Data bit rate up to 8 Mb/s

- AXI4-Lite control interface

- TX and RX Mail box buffers

- Resource optimized IP Core – consume low resource in FPGA/ASIC

- IP Product Guide (PGL202) – Link

- AXI CAN Classic IP Core

- IP Core based on CAN Classic Protocol

- It supports bit rate upto 1 Mb/s

- Targeted for Automotive and Industrial Application

- Recommended for old designs or designs targeted for CAN Classic protocol.

- IP Product Guide (PGL201)

- AXI DSI3 IP Core

- Distributed System Interface (DSI3)

- IP Core Targeted for Automotive Safety Critical Systems.

- IP Core based on DSI3 Bus Standard (Revision 1.00, 2011). DSI3 Protocol document elmos/denso- Link.

- IP Product Guide (PGL209) – Please write us at info@logictronix.com for DSI3 IP Product Guide.

- AXI LIN Controller IP Core

- Coming soon …

G. Data Transfer – SD and USB IP Cores

- AXI SD Host Controller IP Core – SD 2.0

- SD Host Controller IP Core based on SD version 2.0

- Good for most of medium data throughput designs. Speed is sufficient for majority of vision product, Industrial System and embedded product with FPGA. Also good for media playback system and products, which are camera emulators.

- Speed upto 12.5MBps with 25MHz of clock

- AXI interface IP Core for control and data

- Can be used for any FPGA from any Vendor – RTL IP easy to port to any FPGA device.

- Supports 1-bit and 4-bit SD transactions.

- Cyclic Redundancy Check (CRC) for command and data

- Completely based on SD Association SD protocol specification document.

- AXI SD Host Controller IP Core – SD 3.0 – Coming Soon!

- AXI USB Host Controller IP Core – USB 2.0

- Version 1 going to released soon!

- AXI USB Host Controller IP Core – USB 3.0 – Coming Soon!